# MC.31xx - 8 Channel 12 bit A/D up to 25 MS/s

- CompactPCI 6U format

- 12 bit A/D converter board

- 1 MS/s, 10 Ms/s or 25 MS/s

- 2, 4 or 8 channels per board

- Simultaneously sampling on all channels

- 8 input ranges: ±50 mV up to ± 10 V

- Up to 256 MSample memory

- FIFO mode to RAM or hard disk

- Window and Pulsewidth trigger

- Input offset up to ±100%

- Synchronization possible

- Software SBench for Windows included

- Software SBench for Linux included

# **Product range overview**

| Model   | 1 channel | 2 channels | 4 channels | 8 channels |

|---------|-----------|------------|------------|------------|

| MC.3110 | 1 MS/s    | 1 MS/s     |            |            |

| MC.3111 | 1 MS/s    | 1 MS/s     | 1 MS/s     |            |

| MC.3112 | 1 MS/s    | 1 MS/s     | 1 MS/s     | 1 MS/s     |

| MC.3120 | 10 MS/s   | 10 MS/s    |            |            |

| MC.3121 | 10 MS/s   | 10 MS/s    | 10 MS/s    |            |

| MC.3122 | 10 MS/s   | 10 MS/s    | 10 MS/s    | 10 MS/s    |

| MC.3130 | 25 MS/s   | 25 MS/s    |            |            |

| MC.3131 | 25 MS/s   | 25 MS/s    | 25 MS/s    |            |

| MC.3132 | 25 MS/s   | 25 MS/s    | 25 MS/s    | 25 MS/s    |

## **Software/Drivers**

A large number of drivers and examples are delivered with the board:

- Windows NT/2000 32 bit drivers

- Windows XP/Vista/7/8/10, 32 and 64 bit driver

- Linux 32bit and 64bit drivers

- SBench 6.x Base version for Windows and Linux

- Visual C++/Borland C++ Builder examples

- Borland Delphi examples

- Microsoft Visual Basic & Excel examples

- Python examples

- LabWindows/CVI examples

- LabVIEW drivers and examples

- MATLAB drivers and examples

- Other 3rd party drivers (e.g. VEE,DASYLab) are partly available upon request

### **General Information**

The MC.31xx series allow recording of two, four or eight channels with sampling rates of 1 MS/s, 10 MS/s or 25 MS/s. Due to the proven design a wide variety of 12 bit A/D converter boards for CompactP-CI bus can be offered. These boards are available in several versions and different speed grades making it possible for the user to find an individual solution.

As an option 4 digital inputs per channel can be recorded synchronously. The installed memory of up to 256 MSample will be used for fast data recording. It can be used completely by the currently active chan-

nels. If using slower sampling rates the memory is switched to a FIFO buffer and data will be transferred on-line to the PC memory or to hard disk.

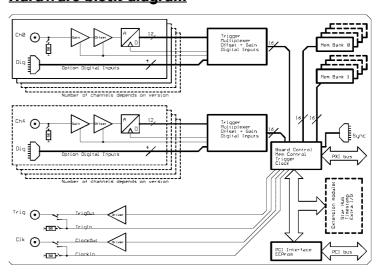

# Hardware block diagram

# Software programmable parameters

| sampling rate                  | 1 kS/s to max sampling rate, external clock, ref clock                                             |  |  |  |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Input Range                    | $\pm 50$ mV, $\pm 100$ mV, $\pm 200$ mV, $\pm 500$ mV, $\pm 1$ V, $\pm 2$ V, $\pm 5$ V, $\pm 10$ V |  |  |  |  |  |

| Input impedance                | 50 Ohm / 1 MOhm                                                                                    |  |  |  |  |  |

| Input Offset                   | ±100% in steps of 1%                                                                               |  |  |  |  |  |

| Clock mode                     | internal PLL, int.quartz, external, ext. divided, ext. reference clock                             |  |  |  |  |  |

| Clock impedance                | 50 Ohm / high impedance (> 4 kOhm)                                                                 |  |  |  |  |  |

| Trigger impedance              | 50 Ohm / high impedance (> 4 kOhm)                                                                 |  |  |  |  |  |

| Trigger mode                   | Channel, External, Software, Auto, Windows, Pulse                                                  |  |  |  |  |  |

| Trigger level                  | 1/256 to 255/256 of input range                                                                    |  |  |  |  |  |

| Trigger edge                   | rising edge, falling edge or both edges                                                            |  |  |  |  |  |

| Trigger pulsewidth             | 1 to 255 samples in steps of 1 sample                                                              |  |  |  |  |  |

| Memory depth                   | 16 up to installed memory in steps of 16                                                           |  |  |  |  |  |

| Posttrigger                    | 16 up to 128 M in steps of 16                                                                      |  |  |  |  |  |

| Multiple Recording segmentsize | 16 up to installed memory / 2 in steps of 16                                                       |  |  |  |  |  |

# Possibilities and options

#### **Input impedance**

All inputs could individually be switched by software between 50 Ohm and 1 MOhm input impedance. If using fast signals and high sampling rates or have 50 Ohm cable impedance the use of the 50 Ohm termination is recommended to minimise noise and signal reflections. If using weak signal sources or standard probes the use of the 1 MOhm termination is helpful.

### Ring buffer mode

The ring buffer mode is the standard mode of all oscilloscope instruments. Digitized data is continuously written into a ring memory until a

trigger event is detected. After the trigger, post-trigger samples are recorded and pre-trigger samples can also be stored. The number of pre-trigger samples available simply equals the total ring memory size minus the number of post trigger samples.

#### FIFO mode

The FIFO mode is designed for continuous data transfer between measurement board and PC memory (up to 100 MB/s) or hard disk (up to 50 MB/s). The control of the data stream is done automatically by the driver on interrupt request.

#### **Channel trigger**

The data acquisition boards offer a wide variety of trigger modes. Besides the standard signal checking for level and edge as known from oscilloscopes it's also possible to define a window trigger. All trigger modes can be combined with the pulsewidth trigger. This makes it possible to trigger on signal errors like too long or too short pulses.

## External trigger I/O

All instruments can be triggered using an external TTL signal. It's possible to use positive or negative edge also in combination with a programmable pulse width. An internally recognised trigger event can - when activated by software - be routed to the trigger connector to start external instruments.

## Pulse width

Defines the minimum or maximum width that a trigger pulse must have to generate a trigger event. Pulse width can be combined with channel trigger, pattern trigger and external trigger.

#### **Multiple Recording**

The Multiple Recording mode allows the recording of several trigger events without restarting the hardware. With this option very fast repetition rates can be achieved. The

on-board memory is divided in several segments of same size. Each of them is filled with data if a trigger event occurs.

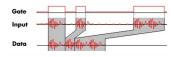

# **Gated Sampling**

The Gated Sampling mode allows data recording controlled by an external gate signal. Data is only recorded if the gate signal has a pro-

grammed level.

#### External clock I/O

Using a dedicated connector a sampling clock can be fed in from an external system. It's also possible to output the internally used sampling clock to synchronise external equipment to this clock.

### Reference clock

The option to use a precise external reference clock (typically 10 MHz) is necessary to synchronize the instrument for high-quality

measurements with external equipment (like a signal source). It's also possible to enhance the stability of the sampling clock in this way. The driver automatically generates the requested sampling clock from the fed in reference clock.

### **Digital inputs**

This option acquires additional synchronous digital channels phase-stable with the analog data. When the option is installed there are 4 additional digital in-

puts for every analog A/D channel.

### **Cascadina**

The cascading option synchronises up to 4 Spectrum boards internally. It's the easiest way to build up a multi channel system. There is a phase delay between two boards of about 500 pico seconds when this synchronisation option is used.

### Star-Hub

The star-hub is an additional module allowing the phase stable synchronisation of up to 16 boards. Independent of the number of boards there is no phase delay between all channels. The star hub distributes trigger and clock information between all boards. As a result all connected boards are running with the same clock and the same trigger.

# Extra I/O

The Extra I/O module adds 24 additional digital I/O lines and 4 analog outputs on an extra connector. These additional lines are independent from the standard function and can be controlled asynchronously. There is also an internal version available with 16 digital I/Os and 4 analog outputs that can be used directly at the rear board connector.

### **Timestamp**

The timestamp function writes the time positions of the trigger events in an extra memory. The timestamps are relative to the start of recording, a defined zero time, ex-

ternally synchronized to a radio clock, an IRIG-B a GPS receiver. Using the external synchronization gives a precise time relation for acquisitions of systems on different locations.

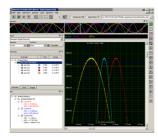

#### SBench 6

A base license of SBench 6, the easy-to-use graphical operating software for Spectrum cards, is included in the delivery. The base license makes it is possible to test the card, display acquired data and make some basic measurements. It's a valuable tool for checking the card's performance and assisting with the unit's initial

setup. The cards also come with a demo license for the SBench 6

professional version. This license gives the user the opportunity to test the additional features of the professional version with their hardware. The professional version contains several advanced measurement functions, such as FFTs and X/Y display, import and export utilities as well as support for all acquisition modes including data streaming. Data streaming allows the cards to continuously acquire data and transfer it directly to the PC RAM or hard disk. SBench 6 has been optimized to handle data files of several GBytes. SBench 6 runs under Windows as well as Linux (KDE, GNOME and Unity) operating systems. A test version of SBench 6 can be downloaded directly over the internet and can run the professional version in a simulation mode without any hardware installed. Existing customers can also request a demo license for the professional version from Spectrum. More details on SBench 6 can be found in the SBench 6 data sheet.

# **Technical Data**

Resolution 12 bit 160 x 233 mm (Standard 6U) Dimension Differential linearity error < 1 ISB (ADC) Width (Standard) 1 slot Width (with digital inputs) Integral linearity error ≤ 2.5 LSB (ADC) 2 slots Multi: Trigger to 1st sample delay 3 mm SMB male Multi: Recovery time < 20 samples Input impedance 50 Ohm / 1 MOhm | | 25 pF ±5 V ext. Trigger accuracy 1 Samples Overvoltage protection (range  $\leq \pm 1 \text{ V}$ ) ±50 V int. Trigger accuracy 1 Sample Overvoltage protection (range  $> \pm 1 \text{ V}$ ) Ext. clock: delay to internal clock 42 ns ±2 ns Warm up time 10 minutes input signal with 50 ohm termination max 5 V rms Operating temperature 0°C to 50°C 110 Ohm @ 2.5 V -10°C to 70°C Digital Inputs input impedance Storage temperature Digital Inputs delay to analog sample -4 samples Humidity 10% to 90% Min internal clock 1 kS/s MTRF 100000 hours Power consumption 3.3 V @ full speed max. 1.69 A (5.6 Watt) Min external clock 1 kS/s Power consumption 5 V @ full speed max. 1.97 A (9.9 Watt) Low: -0.5 > level < 0.8 V High: 2.0 V > level < 5.5 V Trigger input:Standard TTL level Clock input: Standard TTL level High: 2.0 V > level < 5.5 V Trigger pulse must be valid ≥ 2 clock periods. Rising edge. Duty cycle: 50% ± 5% Standard TTL, capable of driving 50 Ohm. Clock output Standard TTL, capable of driving 50 Ohm Trigger output Low < 0.4 V (@ 20 mA, max 64 mA)High > 2.4 V (@ -20 mA, max -48 mA)Low < 0.4 V (@ 20 mA, max 64 mA)High > 2.4 V (@ -20 mA, max -48 mA)One positive edge after the first internal trigger

| Input range                                    | ±50 mV                      | ±100 mV   | ±200 mV   | ±500 mV   | ±1 V      | ±2 V      | ±5 V      | ±10 V     |  |

|------------------------------------------------|-----------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|

| Software programmable offset                   | ±50 mV                      | ±100 mV   | ±200 mV   | ±500 mV   | ±1 V      | ±2 V      | ±5 V      | ±10 V     |  |

| Offset error                                   | < 1 LSB, adjustable by user |           |           |           |           |           |           |           |  |

| Gain error                                     | < 1 %                       | < 1 %     | < 1 %     | < 1 %     | < 1 %     | < 1 %     | < 1 %     | < 1 %     |  |

| Noise (rms): 50 Ohm, 25 MS/s                   | < 1.5 LSB                   | < 1.2 LSB | < 1.0 LSB |  |

| Crosstalk 500 kHz signal, ±50 mV input, 50 Ohm | < -70 dB                    |           |           |           |           |           |           |           |  |

|                    | MC.3110<br>MC.3111 | MC.3112   | MC.3120<br>MC.3121 | MC.3122 | MC.3130<br>MC.3131 | MC.3132    |

|--------------------|--------------------|-----------|--------------------|---------|--------------------|------------|

| max internal clock | 1 MS/s             | 1 MS/s    | 10 MS/s            | 10 MS/s | 25 MS/s            | 25 MS/s    |

| max external clock | 1 MS/s             | 1 MS/s    | 10 MS/s            | 10 MS/s | 25 MS/s            | 25 MS/s    |

| -3 dB bandwidth    | > 500 kHz          | > 500 kHz | > 5 MHz            | > 5 MHz | > 10.0 MHz         | > 10.0 MHz |

### **Dynamic Parameters**

|                        | MC.3110<br>MC.3111 | MC.3112    | MC.3120<br>MC.3121 | MC.3122    | MC.3130<br>MC.3131 | MC.3132    |

|------------------------|--------------------|------------|--------------------|------------|--------------------|------------|

| Test - Samplerate      | 1 MS/s             | 1 MS/s     | 10 MS/s            | 10 MS/s    | 25 MS/s            | 25 MS/s    |

| Testsignal frequency   | 90 kHz             | 90 kHz     | 1 MHz              | 1 MHz      | 1 MHz              | 1 MHz      |

| SNR (typ)              | > 67.5 dB          | > 66.9 dB  | > 64.9 dB          | > 64.9 dB  | > 63.1 dB          | > 62.4 dB  |

| THD (typ)              | < -62.8 dB         | < -62.8 dB | < -62.5 dB         | < -62.5 dB | < -62.5 dB         | < -62.5 dB |

| SFDR (typ), excl harm. | > 80.8 dB          | > 80.5 dB  | > 80.5 dB          | > 78.5 dB  | > 79.5 dB          | > 79.3 dB  |

| SINAD (typ)            | > 61.5 dB          | > 61.4 dB  | > 60.5 dB          | > 60.5 dB  | > 59.8 dB          | > 59.4 dB  |

| ENOB (based on SINAD)  | > 9.9 LSB          | > 9.9 LSB  | > 9.8 LSB          | > 9.8 LSB  | > 9.6 LSB          | > 9.6 LSB  |

Dynamic parameters are measured at ± 1 V input range (if no other range is stated) and 50 Ohm termination with the samplerate specified in the table. Measured parameters are averaged 20 times to get typical values. Test signal is a pure sine wave of the specified frequency with > 99% amplitude. SNR and RNS noise parameters may differ depending on the quality of the used PC. SNR = Signal to Noise Ratio, THD = Total Harmonic Distortion, SFDR = Spurious Free Dynamic Range, SINAD = Signal Noise and Distortion, ENOB = Effective Number of Bits. For a detailed description please see application note 002.

### Order information

The card is delivered with 32 MSample on-board memory and supports standard mode (Scope) and FIFO mode (streaming). Operating system drivers for Windows/Linux 32 bit and 64 bit, examples for C/C++, LabVIEW (Windows), MATLAB (Windows), LabWindows/CVI, Delphi, Visual Basic, Python and a Base license of the oscilloscope software SBench 6 are included. Drivers for other 3rd party products like VEE or DASYLab may be available on request.

| <u>Versions</u>   | Order no.                                     | 1 channe              | l 2 chan              | nels 4 cha             | nnels 8 c           | hannels              |                     |                  |

|-------------------|-----------------------------------------------|-----------------------|-----------------------|------------------------|---------------------|----------------------|---------------------|------------------|

|                   | MC.3110                                       | 1 MS/s                | 1 MS/                 | s                      |                     |                      |                     |                  |

|                   | MC.3111                                       | 1 MS/s                | 1 MS/                 |                        |                     |                      |                     |                  |

|                   | MC.3112                                       | 1 MS/s                | 1 MS/                 | s 1 MS,                | /s 1 <i>N</i>       | AS/s                 |                     |                  |

|                   | MC.3120                                       | 10 MS/s               | 10 MS                 | /s                     |                     |                      |                     |                  |

|                   | MC.3121                                       | 10 MS/s               | 10 MS                 | /s 10 M                | S/s                 |                      |                     |                  |

|                   | MC.3122                                       | 10 MS/s               | 10 MS                 | /s 10 M                | S/s 10              | MS/s                 |                     |                  |

|                   | MC.3130                                       | 25 MS/s               | 25 MS                 | /s                     |                     |                      |                     |                  |

|                   | MC.3131                                       | 25 MS/s               | 25 MS                 | /s 25 M                | S/s                 |                      |                     |                  |

|                   | MC.3132                                       | 25 MS/s               | 25 MS                 | /s 25 M                | S/s 25              | MS/s                 |                     |                  |

| <u>Memory</u>     | Order no.                                     |                       |                       |                        |                     |                      |                     |                  |

|                   | MC.3xxx-64M                                   | Memory                | upgrade to 64 MSa     | imple (128 MB) of to   | tal memory          |                      |                     |                  |

|                   | MC.3xxx-128M                                  | Memory                | upgrade to 128 MS     | sample (256 MB) of t   | otal memory         |                      |                     |                  |

|                   | MC.3xxx-256M                                  | Memory                | upgrade to 256 MS     | sample (512 MB) of t   | otal memory         |                      |                     |                  |

|                   | MC.3xxx-up                                    | Addition              | al fee for later memo | ory upgrade            |                     |                      |                     |                  |

| <b>Options</b>    | Order no.                                     | Option                |                       |                        |                     |                      |                     |                  |

|                   | MC.3xxx-dig                                   | Addition              | al synchronous digit  | al inputs (4 per analo | og channel) includi | ıg Cab-d40-idc-100   |                     |                  |

|                   | MC.3xxx-cs                                    | Option C              | ascading: Synchror    | nization of up to 4 ca | rds (one option ne  | eded per system)     |                     |                  |

|                   | MC.3xxx-smod (1)                              | Option S              | tar-Hub:Synchroniza   | ation of up to 16 card | ds (one option need | ed per system)       |                     |                  |

|                   | MC.3xxx-time (1)                              | Option Ti             | mestamp: Recording    | g of trigger timestam  | os in an extra mem  | ory                  |                     |                  |

|                   | MC.xxxx-xmf (1)                               |                       |                       | al connector, 24 dig   | ital I/O + 4 analog | outputs. Including o | one cable           |                  |

|                   |                                               | Cab-d40               | idc-100.              |                        |                     |                      |                     |                  |

| <u>Cables</u>     |                                               |                       | Order no.             |                        |                     |                      |                     |                  |

| <u> </u>          | for Connections                               | Length                | to BNC male           | to BNC female          | to SMA male         | to SMA female        | to SMB female       |                  |

|                   | Analog/Clock/Trigger                          | 80 cm                 | Cab-3f-9m-80          | Cab-3f-9f-80           | Cab-3f-3mA-80       | Cab-3f-3fA-80        | Cab-3f-3f-80        |                  |

|                   | Analog/Clock/Trigger                          | 200 cm                | Cab-3f-9m-200         | Cab-3f-9f-200          | Cab-3f-3mA-200      | Cab-3f-3fA-200       | Cab-3f-3f-200       |                  |

|                   | Probes (short)                                | 5 cm                  |                       | Cab-3f-9f-5            |                     |                      |                     |                  |

|                   |                                               |                       | to 2x20 pole IDC      | to 40 pole FX2         |                     |                      |                     |                  |

|                   | Digital signals (option)                      | 100 cm                | Cab-d40-idc-100       |                        |                     |                      |                     |                  |

| - 100             |                                               |                       |                       |                        |                     |                      |                     |                  |

| <u>Amplifiers</u> | Order no.                                     | Bandwid               |                       | Input Imped            |                     | Amplification        |                     |                  |

|                   | SPA.1841 (2)                                  | 2 GHz                 | SMA                   | 50 Ohm                 | AC                  | x100 (40 dB)         |                     |                  |

|                   | SPA.1801 (2)                                  | 2 GHz                 | SMA                   | 50 Ohm                 | AC                  | x10 (20 dB)          |                     |                  |

|                   | SPA.1601 (2)                                  | 500 MH                | z BNC                 | 50 Ohm                 | DC                  | ×10 (20 dB)          |                     |                  |

|                   | SPA.1412 (2)                                  | 200 MH:               | z BNC                 | 1 MOhm                 | AC/DC               | x10/x100 (20         | /40 dB)             |                  |

|                   | SPA.1411 (2)                                  | 200 MH:               | z BNC                 | 50 Ohm                 | AC/DC               | x10/x100 (20         | /40 dB)             |                  |

|                   | SPA.1232 (2)                                  | 10 MHz                | BNC                   | 1 MOhm                 | AC/DC               | x100/x1000 (         | 40/60 dB)           |                  |

|                   | SPA.1231 (2)                                  | 10 MHz                | BNC                   | 50 Ohm                 | AC/DC               | x100/x1000 (         | 40/60 dB)           |                  |

|                   | Information                                   | External              | Amplifiers with one   | channel, BNC/SMA       | female connections  | on input and outpu   | t, manually adjusta | ble offset, man- |

|                   | 'AC is included. Plea<br>ctor type for your A |                       | r an adapter          |                        |                     |                      |                     |                  |

|                   |                                               | malening ine conne    | cior type for your A  | , b cara inpui.        |                     |                      |                     |                  |

| Software SBench6  | Order no.                                     |                       |                       |                        |                     |                      |                     |                  |

|                   | SBench6                                       |                       |                       | very. Supports stando  |                     |                      |                     |                  |

|                   | SBench6-Pro                                   | nal version for one o | card: FIFO mode, exp  | oort/import, calcul    | ition functions     |                      |                     |                  |

|                   | SBench6-Multi                                 | les multiple synchro  | nized cards in one    | system.                |                     |                      |                     |                  |

$<sup>^{\</sup>left( 1\right) }$  : Just one of the options can be installed on a card at a time.

Volume Licenses

### Technical changes and printing errors possible

Please ask Spectrum for details.

Sench, digitizerNETBOX and generatorNETBOX are registered trademarks of Spectrum Instrumentation GmbH. Microsoft, Visual C++, Visual Basic, Windows 98, Windows NT, Windows 2000, Windows XP, Windows VI, Windows VI, Windows NT, Windows

<sup>(2) :</sup> Third party product with warranty differing from our export conditions. No volume rebate possible.